- 您现在的位置:买卖IC网 > Sheet目录369 > W9864G6JH-6I (Winbond Electronics)IC SDRAM 64MBIT 54TSOPII

W9864G6JH

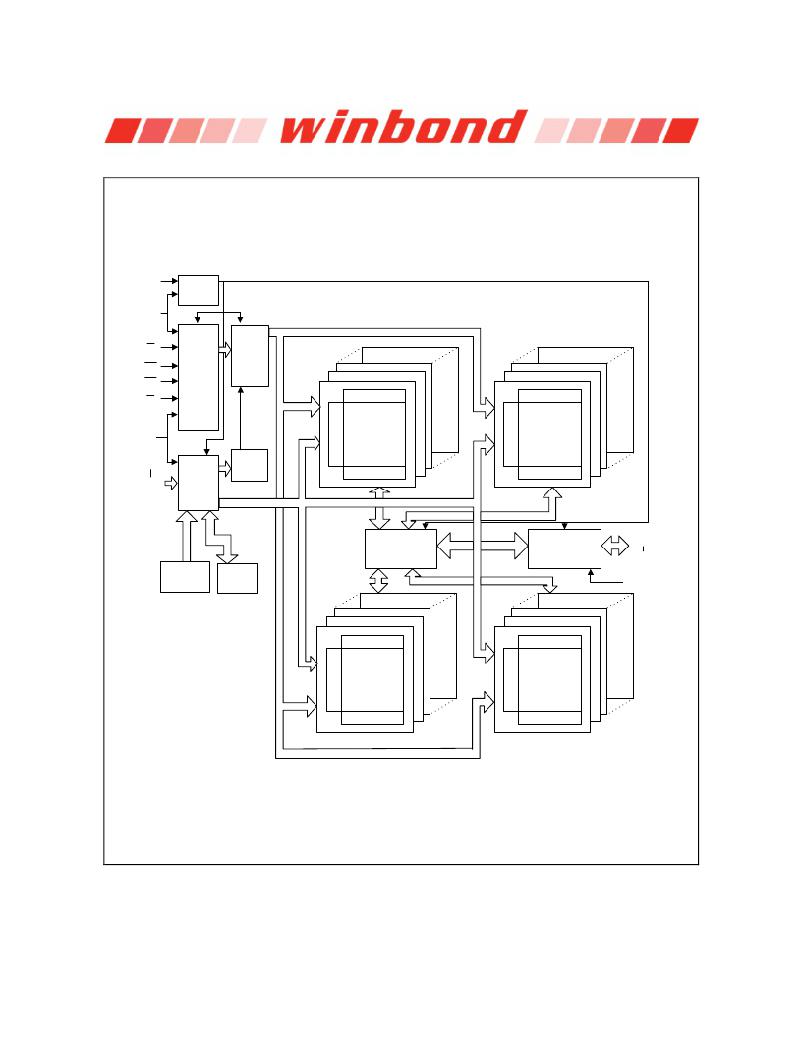

6. BLOCK DIAGRAM

CLK

CLOCK

BUFFER

CKE

CONTROL

CS

SIGNAL

RAS

COMMAND

GENERATOR

CAS

DECODER

WE

A10

COLUMN DECODER

CELL ARRAY

BANK #0

COLUMN DECODER

CELL ARRAY

BANK #1

A0

A9

A11

ADDRESS

BUFFER

MODE

REGISTER

SENSE AMPLIFIER

SENSE AMPLIFIER

BS0

BS1

DATA CONTROL

CIRCUIT

DQ

BUFFER

DQ0

DQ15

REFRESH

COUNTER

COLUMN

COUNTER

NOTE:

UDQM

LDQM

COLUMN DECODER

COLUMN DECODER

CELL ARRAY

CELL ARRAY

BANK #2

BANK #3

SENSE AMPLIFIER

SENSE AMPLIFIER

The cell array configuration is 4096 * 256 * 16

Publication Release Date: Jun. 25, 2013

-6-

Revision A04

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

WM-5614

CABINET WALL MOUNT 37.25X17.9"

WRR-2244

RACK WALL MOUNT RELAY 42" X 19"

WRR-2264

RACK WALL MOUNT 75.25" X 19"

X28C512JIZ-12

IC EEPROM 512KBIT 120NS 32PLCC

X28HC256SIZ-90

IC EEPROM 256KBIT 90NS 28SOIC

X28HC64JIZ-90

IC EEPROM 64KBIT 90NS 32PLCC

XCARD XK-1A

DEV KIT EVENT-DRIVEN PROC XS1-L1

XCARD XTAG-2

ADAPTER USB DEBUGGER JTAG XSYS2

相关代理商/技术参数

W9864G6JH-6I/TRAY

制造商:Winbond Electronics Corp 功能描述:

W9864G6JH-7

制造商:WINBOND 制造商全称:Winbond 功能描述:Self Refresh Current: Standard and Low Power, Sequential and Interleave Burst

W9864G6JH-7S

制造商:WINBOND 制造商全称:Winbond 功能描述:Self Refresh Current: Standard and Low Power, Sequential and Interleave Burst

W9864G6JT

制造商:WINBOND 制造商全称:Winbond 功能描述:1M ? 4 BANKS ? 16 BITS SDRAM

W9864G6JT-6

制造商:Winbond Electronics Corp 功能描述:IC SDRAM 64MBIT 166MHZ 制造商:Winbond Electronics Corp 功能描述:IC SDRAM 64MBIT 166MHZ 54TFBGA

W987D2HB

制造商:WINBOND 制造商全称:Winbond 功能描述:128Mb Mobile LPSDR

W987D2HBGX6E

制造商:WINBOND 制造商全称:Winbond 功能描述:128Mb Mobile LPSDR

W987D2HBGX6I

制造商:WINBOND 制造商全称:Winbond 功能描述:128Mb Mobile LPSDR